目次

半導体製造の概要

半導体とは

半導体とは、電気の導電性が金属と絶縁体の中間に位置する物質であり、特にシリコン(Si)が最も一般的に使用される材料です。半導体の特性を活かし、電子機器や集積回路(IC)の基盤として多くの製品に利用されています。半導体材料は、その電気的特性を外部の影響で変化させることができるため、スイッチングや増幅などの機能を持つデバイスを作成することができます。半導体製造工程の流れ

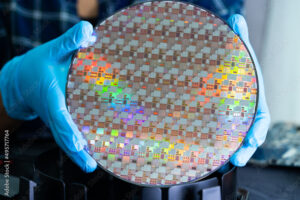

半導体の製造工程は非常に精密で複雑です。主に以下のステップで進行します:- ウェハー作成: シリコンの原料から薄い円盤状のウェハー(基板)を切り出します。

- 酸化: ウェハーの表面に酸化シリコンを形成し、絶縁層を作成します。

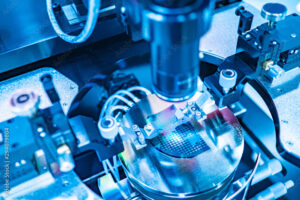

- フォトリソグラフィ: 紫外線光を使って、ウェハーの表面にマスクを重ね、回路パターンを転写します。

- エッチング: フォトリソグラフィで転写した回路パターンを、化学薬品やプラズマで刻み込みます。

- ドーピング: 特定のエリアに不純物を加えることで、半導体の電気的特性を調整します。

- メタライゼーション: 金属を蒸着し、回路を接続するための配線を形成します。

- テスト・パッケージング: 完成したチップを検査し、最終的なパッケージに封入します。

半導体の微細化の重要性

半導体の微細化は、集積回路の性能向上と密度の増加をもたらすため、半導体産業において非常に重要です。微細化により、1つのチップにより多くのトランジスタを配置でき、処理速度の向上、消費電力の削減、機能の向上が実現します。 微細化が進むことで、半導体の処理能力は指数関数的に向上し、より小型で高性能なデバイスの製造が可能となります。しかし、微細化には製造技術の進化や新しい材料の開発、そして製造プロセスの精密化が求められます。現在の技術では、最先端の半導体チップは7nm(ナノメートル)や5nmの微細化が達成されており、更なる微細化が次世代技術の鍵となっています。成膜プロセスの基礎

成膜とは

成膜とは、基板の表面に薄い膜を形成するプロセスで、電子機器や光学デバイス、半導体デバイスなどの製造において重要な技術です。成膜によって、基板の物理的特性や化学的特性、電気的特性を改善したり、保護したりすることができます。成膜は主に、化学的または物理的な方法で膜を基板に付着させる技術を指します。 成膜の主な目的としては、次のようなものがあります:- 機械的保護: 基板を外的な衝撃や摩耗から保護

- 電気的・光学的特性の付与: 電気伝導性や光透過性の向上

- 化学的特性の変更: 表面の反応性や耐食性の向上

- 密着性の向上: 異なる材料間の接着強度を高める

成膜プロセスの種類

成膜プロセスは大きく分けて、物理的成膜と化学的成膜の2つに分類されます。以下は主な成膜技術です:- 物理蒸着(PVD)

物理的な方法で材料を蒸発させ、基板上に薄膜を形成する技術です。代表的な方法には、蒸発法とスパッタリング法があります。

- 蒸発法: 金属や絶縁体を高温で蒸発させ、基板に薄膜を形成します。

- スパッタリング法: 基板上にイオンを衝突させ、ターゲット材料から原子を飛ばして膜を作ります。

- 化学蒸着(CVD)

化学反応を利用して気体状の化学物質を基板上に反応させ、薄膜を生成する技術です。代表的な方法には、低圧CVD(LPCVD)、熱CVD、プラズマCVDなどがあります。

- 低圧CVD(LPCVD): 高温で化学反応を促進し、薄膜を基板に堆積させます。

- プラズマCVD: プラズマを使用して化学反応を起こし、薄膜を基板に形成します。

- 原子層堆積(ALD) 1原子層ずつ順次積み重ねる方法で、非常に薄い膜を高精度に作ることができます。ナノメートル単位の厚さを制御できるため、特に微細構造に対応する際に使用されます。

成膜技術の進化

成膜技術は、電子デバイスの高性能化や省エネルギー化に対応するために進化してきました。特に、微細化が進む半導体やMEMS(微小電子機械システム)デバイスの製造において、より精密で均一な成膜が求められています。 近年の進化としては、以下のような点があります:- ナノメートルスケールでの精密な制御: 微細構造の設計に合わせた高精度な膜形成技術(例:原子層堆積(ALD)の進化)

- 省エネルギーで環境に配慮した技術: プラズマCVDや低温で動作するCVD技術など、環境負荷を軽減しながら高品質な膜を形成する技術

- 新しい材料の開発: 高機能膜材料や、透明、導電性、絶縁性を持つ特殊な膜材料が登場し、特定用途に応じた選択肢が増加

エッチングの役割と仕組み

エッチングとは

エッチングは、基板上に形成された薄膜や素材から、特定の部分を化学的または物理的な手法で選択的に除去するプロセスです。主に半導体製造やプリント基板の製造において利用され、微細なパターンや構造を作成するための重要な工程です。エッチングは、金属、絶縁体、半導体など、さまざまな材料に対して使用されます。 エッチングの主な目的には、次のことが挙げられます。- 微細パターンの作成: 回路パターンやデバイスの構造を基板上に形成

- 不要部分の除去: 不要な材料を選択的に除去して、デバイスの機能を最適化

- 表面加工: 基板や膜の表面特性を変更するためにエッチングを行う場合もあります

エッチングの種類と特徴

エッチングには大きく分けて化学的エッチングと物理的エッチングの2種類があります。これらの方法は、それぞれ異なる特徴と適用範囲を持っています。 化学的エッチング(ウェットエッチング) 化学的エッチングは、液体薬品を用いて基板上の材料を除去する方法です。この方法は均一なエッチングが可能で、低コストで簡単に実施できるため、多くの用途に使用されます。主に酸性やアルカリ性の溶液が使用され、特定の薬品が材料ごとに選ばれます。- 特徴: 簡単で低コスト、広範囲な材料に適用可能

- 用途: 金属や半導体デバイス、プリント基板の製造

- 特徴: 微細なパターンの作成に適し、方向性のあるエッチングが可能

- 用途: 高精度な半導体製造やMEMSデバイスの作成

- 特徴: 非接触で精密な加工が可能、高解像度

- 用途: 特殊な素材の加工や微細パターン作成

エッチングプロセスの流れ

エッチングプロセスは、いくつかの段階を経て行われます。以下の手順で進行します。 1. マスクの作成 まず、基板上に保護膜(マスク)を形成します。このマスクはエッチングを行いたくない部分を保護し、エッチングすべき部分だけを露出させる役割を担います。通常、フォトリソグラフィ技術を使ってマスクが作成されます。 2. エッチング マスクで保護されていない部分に、化学薬品やプラズマを使ってエッチングを行います。これにより、指定された部分の材料が選択的に除去され、パターンが基板に形成されます。 3. マスクの除去 エッチングが終了した後、マスクを取り除きます。この工程では、マスクの素材に応じた除去方法が使用されます。 4. 仕上げと検査 最後に、エッチング後のパターンが正確かどうかを検査します。検査の結果、必要に応じて追加の処理や微調整を行います。この工程では、精度や品質を確保するための最終確認が行われます。 このように、エッチングは精密な加工を実現するために不可欠なプロセスです。特に半導体製造や電子機器の製造において、エッチングは非常に重要な役割を果たしています。半導体の成膜技術

半導体製造における成膜技術は、薄膜を基板上に高精度で形成するために不可欠なプロセスです。これらの技術は、デバイス性能や製造コストに大きな影響を与えるため、選定と制御が非常に重要です。以下では、代表的な成膜技術を解説します。物理的気相成長(PVD)

物理的気相成長(PVD)は、物理的な方法を使用して気体状の材料を基板上に堆積するプロセスです。一般的に、材料は蒸発またはスパッタリングによって気体状になり、基板上に薄膜を形成します。PVDは、主に金属膜の成膜に使用され、精密な膜厚の制御が可能です。 特徴- 精密な膜厚制御が可能

- 高い密着性の金属膜を作成

- 銅、アルミニウム、金などの金属膜が主に使用

- 半導体製造

- 電気回路の接続層形成

- 表面コーティング

化学気相成長(CVD)

化学気相成長(CVD)は、ガス状の前駆体を基板上で化学反応させて固体の薄膜を形成する技術です。高温で反応が進行し、基板表面に化学的に結びついた薄膜が堆積します。CVDは、絶縁膜や半導体膜など多くの材料に利用されます。 特徴- 広範囲な材料に対応可能(絶縁体、半導体、金属)

- 高い膜品質と均一性が得られる

- 高温プロセスが必要

- 半導体のチップ製造

- 太陽光パネルやディスプレイ製造

- 薄膜トランジスタ

アトミックレイヤー堆積(ALD)

アトミックレイヤー堆積(ALD)は、単一の原子層単位で非常に薄い膜を積み重ねていく技術です。前駆体をガス状で供給し、表面との化学反応で膜が形成され、次に新しい前駆体を供給して次の層を形成します。このプロセスは原子レベルで制御され、非常に薄い均一な膜を作成できます。 特徴- 極薄膜の高精度な形成

- 高い膜均一性と精度

- 他の成膜技術に比べてスケールアップが難しい

- 高精度なデバイス製造

- バッテリーの電極膜

- ナノテクノロジー

分子ビームエピタキシー(MBE)

分子ビームエピタキシー(MBE)は、非常に高真空下で、単一分子または原子ビームを基板上に堆積させる成膜技術です。MBEは、非常に精密な膜厚制御と高品質の単結晶膜を作成することができます。エピタキシャル成長に使用されるため、半導体デバイスの高精度な製造に適しています。 特徴- 高真空環境での成膜

- 原子単位での精密な制御

- 高品質な単結晶膜を得られる

- 高精度な半導体デバイス製造

- LEDやレーザーの製造

- ナノデバイス技術

電解成長と電気泳動成長

電解成長は、電解質溶液中で電流を使用して金属を基板に堆積させるプロセスです。電気泳動成長は、基板に電場をかけて、溶液中の粒子を基板に引き寄せて成膜を行います。これらは、主に金属材料の成膜に使用されることが多い技術です。 特徴- 電気化学的な反応を利用

- 高い膜密着性と高分解能が得られる

- コストが低くスケールアップが容易

- 金属膜の成膜

- 精密部品のコーティング

- 電子機器の製造

半導体製造における薄膜の役割

半導体製造では、薄膜が重要な役割を果たしており、さまざまなプロセスで使用されています。薄膜技術は、半導体デバイスの機能性や性能を決定するため、精密な制御が求められます。以下に薄膜の基本、種類、特性、応用について詳述します。薄膜の基本

薄膜とは、基板表面に非常に薄い層で形成された材料のことです。通常、厚さは数ナノメートルから数ミクロンの範囲で、材料や成膜方法によって異なる特性を持ちます。半導体製造における薄膜技術は、回路やデバイスの製造、絶縁、導電性、反射防止など、多くの用途に使用されています。 薄膜の形成には、物理的気相成長(PVD)、化学気相成長(CVD)、アトミックレイヤー堆積(ALD)など、さまざまな成膜技術が利用されています。これらの薄膜層は、半導体チップ内で複数の層として形成され、それぞれが異なる機能を持ちます。薄膜の種類と特性

半導体製造において利用される薄膜の種類は主に以下の通りです。- 導電性薄膜

- 電気を通す特性を持つ金属や導電性高分子が使用されます。主に配線や接続、トランジスタのソース・ドレイン領域などに使用されます。

- 絶縁性薄膜

- 電気を通さない絶縁材料、例えばシリコン酸化膜(SiO2)や窒化シリコン(Si3N4)などが使用されます。これらはトランジスタのゲート酸化膜やバリア層、キャパシタの絶縁層などとして使用されます。

- 半導体薄膜

- シリコンやゲルマニウムなどの半導体材料を使用しており、集積回路や光通信デバイスに利用されます。これらは半導体素子の形成に重要な役割を果たします。

- 光学薄膜

- 特定の波長の光を反射したり透過させたりする特性を持ち、反射防止膜やフィルタ膜などが使用されます。主に光デバイスやディスプレイ、太陽光パネルのコーティングに利用されます。

薄膜の応用と例

薄膜は半導体製造において数多くの重要な応用を持っています。代表的な例として、以下のような応用があります。- トランジスタと集積回路の形成 薄膜はトランジスタのゲート酸化膜や金属配線層として使用され、これによりトランジスタの動作を制御し、集積回路が形成されます。

- 太陽光パネル 薄膜太陽電池は、光を吸収して電力を生成するために、シリコン薄膜や化合物半導体薄膜を使用します。

- ディスプレイ技術 液晶ディスプレイ(LCD)や有機ELディスプレイ(OLED)などでは、薄膜技術が画素の形成や電気的制御に用いられます。

- センサー技術 温度センサー、圧力センサー、ガスセンサーなどで薄膜が使用され、センサーの感度や精度を向上させるために重要な役割を果たします。

- メモリデバイス DRAMやフラッシュメモリの製造において、薄膜が絶縁層や配線層として使用され、データの保存と読み出しを可能にします。

成膜工程の実際

成膜工程は、半導体製造における重要なプロセスであり、デバイスの機能や性能を大きく左右します。このプロセスでは、さまざまな成膜方法を使用して基板に薄膜を均等に形成します。以下に、成膜工程の設計、成膜装置と操作、品質管理について詳しく説明します。成膜工程の設計

成膜工程の設計は、最終製品の品質と製造効率に直結するため非常に重要です。まず、使用する成膜方法を選定し、その後、プロセス条件(温度、圧力、ガスフローなど)を調整して最適な薄膜を形成します。設計時には以下の要素を考慮します:- 材料選定 成膜する材料は、デバイスの用途や機能に応じて選定します。例えば、導電性、絶縁性、半導体特性を持つ材料を使用することで、デバイスの動作に必要な特性を持たせます。

- 成膜方法の選定 成膜には、物理的気相成長(PVD)、化学気相成長(CVD)、アトミックレイヤー堆積(ALD)などの方法があり、それぞれの方法において異なるプロセス条件や特徴があります。目的に応じて最適な方法を選ぶことが重要です。

- 膜厚と均一性の調整 薄膜の厚さや均一性は、製品の性能に大きな影響を与えます。工程設計では、膜厚の精密な制御が求められます。また、膜厚が均一であることも重要です。

成膜装置と操作

成膜装置は、成膜プロセスを実行するための機器で、さまざまな種類の装置が存在します。それぞれの装置は、選定した成膜方法に基づいて構造が異なり、操作も異なります。代表的な装置には以下のものがあります:- スパッタリング装置(PVD) 高真空環境下でターゲットから材料を蒸発させて基板に薄膜を形成する装置です。スパッタリングは金属膜や導電性膜を形成する際に広く使用されます。

- CVD装置(化学気相成長) 化学反応を利用してガス状の前駆体から固体材料を基板に成膜する装置です。薄膜の均一性が高く、高品質な絶縁膜や半導体膜の形成に使用されます。

- ALD装置(アトミックレイヤー堆積) 極薄膜を高精度で堆積するための装置で、原子レベルで成膜を行うことができます。非常に均一な膜を形成できるため、微細化が進んでいる半導体製造で多く使用されます。

- MBE装置(分子ビームエピタキシー) 高真空中で材料を基板に直接蒸発させて成膜する装置です。高精度な薄膜形成が可能で、特に高性能な半導体デバイスに使用されます。

成膜工程における品質管理

成膜工程における品質管理は、製品の歩留まりや性能を最大限に引き出すために必要不可欠です。主な品質管理項目には以下のものがあります:- 膜厚の測定 成膜した薄膜の厚さは非常に重要なパラメータです。膜厚が均一でないと、デバイスの性能に悪影響を与えます。膜厚を適切に測定するためには、X線反射率測定(XRR)や干渉計測法などの技術が使用されます。

- 膜の密着性と強度 成膜した膜が基板と強固に結びついているかを確認するために、引張試験やスクラッチテストが行われます。密着性が不足していると、デバイスの耐久性が低下する可能性があります。

- 膜の均一性 膜の均一性は、成膜中の温度や圧力、ガスフローなどのプロセス条件に影響されます。均一な膜が形成されているかを確認するために、膜の表面をスキャンして観察します。

- 欠陥の検出 成膜中に発生した欠陥(クラック、気泡、不均一な膜)は、製品の性能に直接影響します。顕微鏡や電子顕微鏡(SEM)を使って膜表面の欠陥を検査します。

- プロセスの再現性 同一条件で繰り返し成膜を行い、製品ごとのバラつきがないかを確認します。再現性が悪い場合、プロセスの調整が必要です。