目次

半導体製造とは:基本概念の理解

半導体の役割と重要性

半導体は、電気の流れを制御する特性を持つ材料であり、現代の電子機器に不可欠な要素です。トランジスタやダイオード、集積回路(IC)など、ほぼすべての電子機器に組み込まれています。半導体の進化は、コンピューター、スマートフォン、通信インフラ、自動車などの性能向上に大きく貢献しており、産業全体の発展を支えています。 特に、半導体技術はデジタルトランスフォーメーション(DX)や人工知能(AI)、モノのインターネット(IoT)といった分野で重要な役割を果たし、現代社会の基盤を支える技術のひとつです。近年では、半導体の微細化や高性能化が進み、エネルギー効率の向上や小型化の実現が求められています。半導体製造プロセスの全体像

半導体製造プロセスは、多くの高度な技術と複雑な工程を含む精密な製造プロセスです。以下のような主要な工程が含まれます。| 工程 | 内容 |

|---|---|

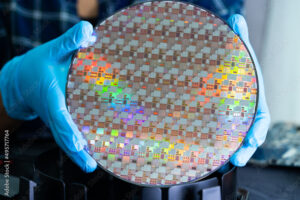

| ウェハ製造 | シリコンインゴットをスライスし、ウェハを作成 |

| フォトリソグラフィ | マスクを使用してウェハ上に回路パターンを形成 |

| 現像 | レジストを露光後、不要な部分を溶解除去 |

| エッチング | ウェハ表面を削り、回路パターンを形成 |

| 拡散・ドーピング | 半導体の特性を制御するため、不純物を導入 |

| 成膜(CVD、PVD) | 絶縁膜や金属配線を形成するための膜を堆積 |

| CMP(化学機械研磨) | ウェハ表面を平坦化し、次工程の精度を確保 |

| 配線形成 | 回路間を接続するための金属配線を作成 |

| パッケージング | ウェハを個別のチップに分割し、外部端子を形成 |

現像プロセスの位置付け

現像プロセスは、フォトリソグラフィ工程の一部であり、回路パターンを形成する重要なステップです。- フォトレジスト塗布:ウェハ表面に光に反応する感光性のフォトレジストを塗布

- 露光:フォトマスクを通して紫外線を照射し、回路パターンを転写

- 現像:露光後、不要なフォトレジストを化学溶液で除去し、パターンを明確化

- エッチング:現像後のパターンを基板へ転写するために不要部分を削除

半導体現像装置の基礎

現像とは?―半導体製造における意義

現像とは、フォトリソグラフィ工程において、露光されたフォトレジストの不要部分を除去し、ウェハ上に回路パターンを形成するプロセスです。半導体製造においては、回路の微細化や高性能化が求められるため、この工程の精度がチップの性能や歩留まりに大きく影響します。特に、現像プロセスの均一性や寸法制御の精度が重要視されており、適切な処理が行われないと、パターンの寸法誤差や欠陥が発生する原因となります。そのため、現像技術の高度化は、半導体業界において不可欠な要素となっています。現像プロセスの目的と機能

現像プロセスの主な目的は、露光によって形成されたフォトレジストのパターンを明確にし、次のエッチングや成膜工程を正確に行うための準備を整えることです。この工程では、不要なレジストを化学的に除去し、ナノメートル単位の精密な寸法制御を実現します。特に、現像液の均一な適用や反応時間の最適化が求められ、これにより回路パターンの精度と安定性が向上します。 また、現像工程の品質が不安定だと、パターンの欠陥や寸法ばらつきが発生し、製造歩留まりの低下につながる可能性があります。そのため、半導体メーカーは現像条件の最適化やプロセス制御技術の強化に力を入れています。現像が適切に行われることで、次工程であるエッチングや成膜がスムーズに進み、高品質な半導体デバイスの製造が可能となります。現像装置の種類と特徴

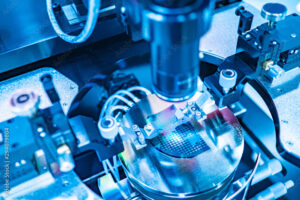

現像装置にはいくつかの種類があり、それぞれの方式によって処理方法や特性が異なります。一般的に使用されるのは、バッチ式現像装置、シングルウェハ式現像装置、スプレー現像装置、浸漬現像装置の4つです。 バッチ式現像装置は、一度に複数のウェハを処理できるため、高スループットを実現できるのが特徴です。大量生産が求められるラインでは、この方式が採用されることが多くなっています。一方、シングルウェハ式現像装置は、一枚ずつウェハを処理するため、より精密な寸法制御が可能です。特に、高い均一性と再現性が求められる先端半導体製造プロセスでは、この方式が優先されます。 スプレー現像装置は、現像液を均一にスプレーすることで、膜厚のばらつきを抑えつつ、安定した現像処理を行うことが可能です。また、浸漬現像装置は、ウェハ全体を液中に浸すことで均一な現像を行い、特に大面積のウェハを処理する場合に有効な方式となっています。 それぞれの装置には特性があり、コストや精度、生産性などの観点から最適なものが選ばれます。半導体製造の進化に伴い、現像装置の技術もさらに発展しており、高精度かつ高効率なプロセスの実現が求められています。現像プロセスの詳細

フォトレジストの塗布方法

フォトレジストの塗布は、半導体製造のフォトリソグラフィ工程における最初のステップであり、ウェハ表面に均一なレジスト膜を形成することが求められます。一般的に、スピンコート法が広く用いられています。この方法では、ウェハ上にフォトレジストを滴下し、高速回転させることで、遠心力を利用して均一な薄膜を形成します。回転速度や時間を調整することで、膜厚をナノメートル単位で制御することが可能です。 また、大面積の基板に対しては、スプレーコート法やスロットダイコート法が用いられることもあります。スプレーコート法は、微細なミスト状のレジストを均一に分散させる技術で、非平坦な表面にも適用できます。一方、スロットダイコート法は、ノズルから一定量のレジストを均一に供給しながら基板上に塗布する方式であり、より高精度な膜厚制御が可能です。いずれの方法でも、フォトレジスト塗布後には、ベーク(予備加熱)を行い、溶媒の揮発と膜の安定化を図ります。露光プロセスの原理と技術

露光プロセスは、フォトマスクを通じて光を照射し、フォトレジストの化学反応を引き起こす工程です。光の波長や照射方法によって、パターンの解像度や精度が決まります。主な露光技術には、以下のようなものがあります。- 紫外線(UV)露光:従来のリソグラフィ技術であり、i線(365nm)やg線(436nm)を使用。微細化が進むにつれ、より短波長の光源が求められる。

- 深紫外線(DUV)露光:KrF(248nm)やArF(193nm)エキシマレーザーを使用し、より微細なパターン形成が可能。

- 極端紫外線(EUV)露光:13.5nmの波長を持つEUV光を使用し、最先端の微細加工技術として活用されている。

現像工程の進行と制御

露光後の現像工程では、フォトレジストの不要部分を選択的に溶解・除去し、回路パターンを明確にします。このプロセスは、主にアルカリ性の現像液を用いたウェット現像方式が一般的です。現像の進行は、以下のステップで構成されます。- 現像液の供給:現像液をウェハ表面に均一に分散させる。

- 現像反応:露光によって化学変化したフォトレジストが現像液によって除去される。

- リンス(洗浄):現像液の残留物や溶解したフォトレジストを純水で洗い流し、パターンの形状を安定化させる。

- 乾燥:ウェハ表面の水分を完全に除去し、次工程へ移行する。

半導体微細化技術の進展

微細化の必要性と課題

半導体の微細化は、デバイスの高性能化と低消費電力化を実現するために不可欠な技術です。トランジスタのサイズを縮小することで、同じチップ面積内により多くの素子を集積でき、演算能力やエネルギー効率の向上につながります。この進展は、ムーアの法則に従い、数十年にわたって継続されてきました。 しかし、微細化が進むにつれて、以下のような課題が顕在化しています。- 量子効果の影響:トランジスタがナノスケールになると、トンネル効果や短チャネル効果などの量子現象が無視できなくなる。

- リソグラフィ技術の限界:従来の深紫外線(DUV)露光技術では、解像度の限界が近づき、EUV(極端紫外線)技術の導入が不可欠になる。

- 配線抵抗と消費電力の増加:配線が細くなることで、電気抵抗が増加し、遅延や発熱の問題が深刻化する。

- 製造コストの上昇:先端ノードへの移行には、新規設備の導入や高度な技術開発が必要であり、開発コストと製造コストが急増する。

EUV露光技術の概要

EUV(Extreme Ultraviolet)露光技術は、波長13.5nmの極端紫外線を利用することで、従来のリソグラフィ技術では困難だった極小パターンの形成を可能にする技術です。従来のArFエキシマレーザー(193nm)と比較して、より短波長であるため、単一露光で数ナノメートルレベルのパターンを描画できます。 EUVリソグラフィの主要な特徴は以下の通りです。- 単一露光で微細パターンを形成:従来のDUV技術では、マルチパターニングを必要としたが、EUVでは単一露光で対応可能。

- 高精度な光学系:EUV光は吸収されやすいため、従来のレンズではなく、多層膜ミラーを使用した反射光学系が採用されている。

- フォトマスクの高精度化:EUV用フォトマスクには高い精度が求められ、欠陥管理が重要となる。

- 光源の低効率:EUV光は生成が困難であり、出力の低さがスループットの向上を妨げる要因となっている。

- 高額な設備投資:EUV露光装置は非常に高価であり、導入コストが莫大となる。

- マスク欠陥の管理:EUV用フォトマスクは、従来の透過型マスクと異なり、欠陥の修正が困難であり、高精度な検査と管理が必要。

EUV技術の現状と未来展望

現在、EUVリソグラフィは5nmプロセスおよび3nmプロセスの量産に本格的に導入されており、TSMC、Samsung、Intelなどの半導体メーカーが積極的に採用を進めています。次世代の2nmノード以降では、さらなるEUV技術の最適化が求められています。 今後のEUV技術の進展において、以下のポイントが注目されています。- 高出力EUV光源の開発:現行のEUV光源は100Wクラスだが、より高いスループットを実現するために、500W以上の高出力光源の開発が進められている。

- ハイNA(高開口数)EUVの導入:現在のEUVシステムは0.33NAだが、より高解像度な0.55NAのEUVリソグラフィが開発中であり、2nm以下の微細加工に対応可能となる。

- マスク欠陥の低減:EUV専用のマスク検査技術や補正技術の進展により、量産レベルでの歩留まり向上が期待される。

- 次世代プロセス技術との統合:ナノシートFETやGAAFET(Gate-All-Around FET)などの新しいトランジスタ構造と組み合わせることで、さらなる高性能化が可能になる。